#### Tecnología Electrónica 3º Ingeniero Aeronáutico

# Introducción a los procesadores digitales de señal (DSPs)

Dra. Ma Ángeles Martín Prats

Curso 2010/2011

#### Reseña histórica

- Años 60: 1<sup>er</sup> procesado de señales digitales en tiempo real, sobre máquinas VAX y DEC PDP.

- Años 70: máquinas de cálculo que usaban chips de lógica discreta (tecnología TTL) y unidad aritmética programable de 4 bits para realizar procesamiento de datos.

- 1980: 1<sup>er</sup> chip moderno (NEC).

- 1982: 1er DSP en tecnología TTL (TMS32010-TI).

- Tecnología CMOS.

# Conceptos básicos (I)

- DSP: microprocesador orientado al procesamiento de señales digitales y a la realización de cálculos a alta velocidad.

- Arquitecturas especiales orientadas a realización hardware de cálculos que otros microprocesadores implementan vía software.

- Hardware CPU más complejo que otros microprocesadores.

- Área Si mayor.

- Coste mayor.

# Conceptos básicos (II)

- Circuitería optimizada para realizar funciones:

- Filtrado.

- Correlación.

- Análisis espectral.

Muchas operaciones típicas del procesado de señal se ejecutan en un único ciclo de instrucción

# Conceptos básicos (III)

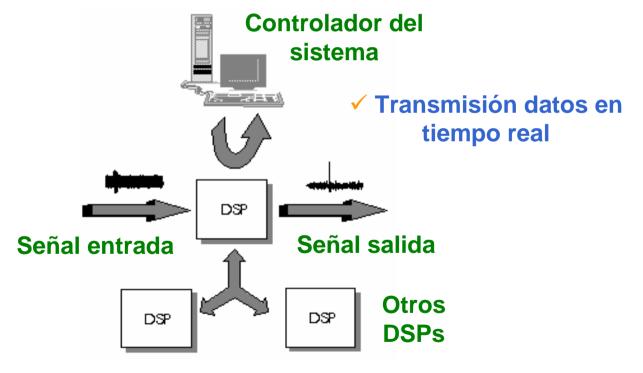

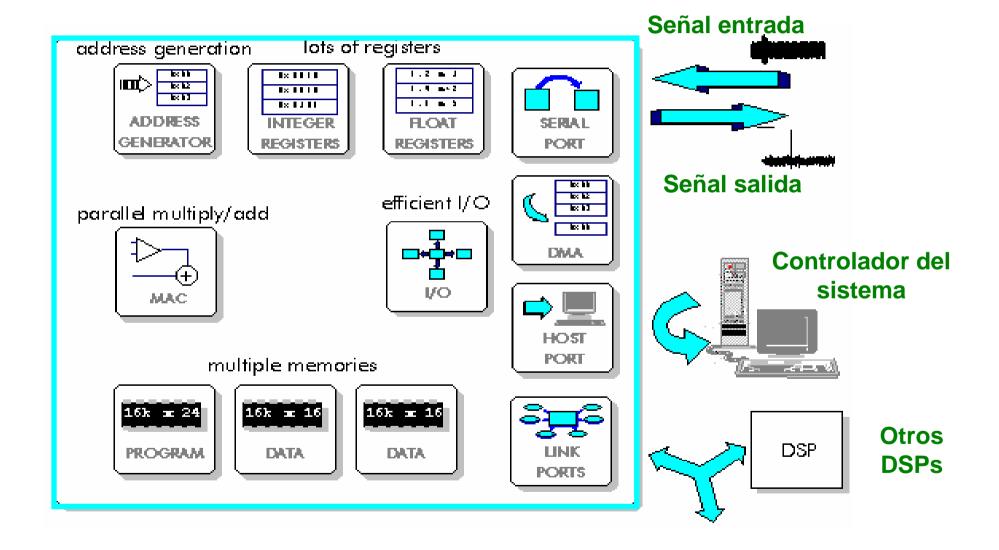

- Se diseñan para ser escalables: operación en paralelo.

- Incorporan periféricos de control, de bloqueo del sistema y periféricos E/S de alta velocidad (puertos serie síncronos permiten conectar varios DSPs para aplicaciones con multiprocesadores).

- DSP más versátil y menor coste de desarrollo que ASICs de función fija o FPGAs.

- Se programan en C o ensamblador.

# **Operaciones típicas DSP**

Requieren funciones específicas:

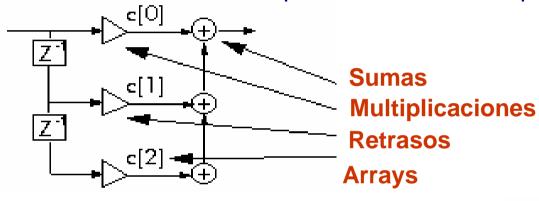

#### Filtro FIR

- Aritmética alta velocidad especializada.

- Transferencia datos tiempo real.

- Arquitecturas de memoria de acceso múltiple.

/40 Suma y multiplicación en paralelo 51

**Procesador DSP32C Lucent**

32 Bus simple

## Grado de paralelismo

Directamente proporcional al número de operaciones que el DSP es capaz de realizar en un ciclo de reloj

- ✓ Mejoras de la arquitectura interna orientadas a aumentar el paralelismo del sistema.

- ✓ DSPs con múltiples

CPU que pueden trabajar en paralelo.

**Ejemplo: TMS320C6201-**

**TI: 200MHz**

Programación de DSP: lenguaje de programación a alto nivel que simplifica el desarrollo del software al usuario.

## Aplicaciones basadas en DSPs

- Telecomunicaciones.

- Control.

- Instrumentación.

- Análisis de imagen y voz.

- Automóvil.

- Medicina.

- Aeronáutica, aerospacial y defensa.

- Etc.

# Líneas Investigación de fabricantes de DSPs

Nuevas arquitecturas, compiladores más inteligentes y mejores herramientas de desarrollo y depuración.

Procesamiento de datos en el menor tiempo posible. Compiladores capaces de optimizar el programa en tiempo de ejecución, tarea que complica el desarrollo de los mismos.

#### Alternativas al uso del DSP

- Ordenador personal → sistema operativo se ejecuta en paralelo con la aplicación de procesado de la señal (fuera de línea).

- Microcontroladores → control de procesos en tiempo real. Se clasifican en función del tamaño del bus de datos. No trabajan en paralelo. Funcionan en solitario.

- FPGA.

# Tabla comparativa de tiempos empleados en la realización de operaciones aritméticas lógicas de DSPs y microcontroladores

| Procesador         | Bus datos | Reloj | ±    | Х    | 1      | <b>√</b> |  |

|--------------------|-----------|-------|------|------|--------|----------|--|

| DSPs               |           | MHz   | ns   | ns   | μs     | μs       |  |

| TMS32010           | 16 bits   | 5     | 200  | 200  | < 12.8 | < 59     |  |

| TMS32020           | 16 bits   | 5     | 200  | 200  | < 3.4  | < 59     |  |

| TMS320C30          | 32 bits   | 33    | 60   | 60   | < 2    | < 2      |  |

| TMS320C40          | 32 bits   | 40    | 50   | 50   | <1     | <1       |  |

| Microcontroladores |           |       |      |      |        |          |  |

| M68HC11            | 8 bits    | 8     | 1000 | 5000 | 20.5   |          |  |

| MCS96              | 16 bits   | 16    | 800  | 1750 | 2.5    |          |  |

| MC68030            | 32 bits   | 20    | 200  | 1400 | 2.8    |          |  |

| IAPX80286          | 32 bits   | 8     | 375  | 3000 | 3.12   | > 2      |  |

| NOVIX4000          | 32 bits   | 8     | 125  | 3130 | 5.62   | 10.62    |  |

# **Ventajas DSPs**

Optimización del hardware para el procesamiento de señales y manejo de datos en tiempo real.

Fácil reconfiguración (código en lenguaje C).

Fácil escalado → procesamiento en paralelo.

# Clasificación de microprocesadores atendiendo a su funcionalidad

- CISC →> 80 instrucciones en código máquina, algunas muy complejas y potentes que precisan muchos ciclos para ejecutarse.

- RISC → pocas instrucciones en código máquina que se ejecutan en un ciclo de trabajo. Permiten optimizar el hardware del sistema.

- SISC → microprocesadores destinados a aplicaciones concretas, instrucciones específicas.

DSPs → CISC y SISC (telefonía móvil)

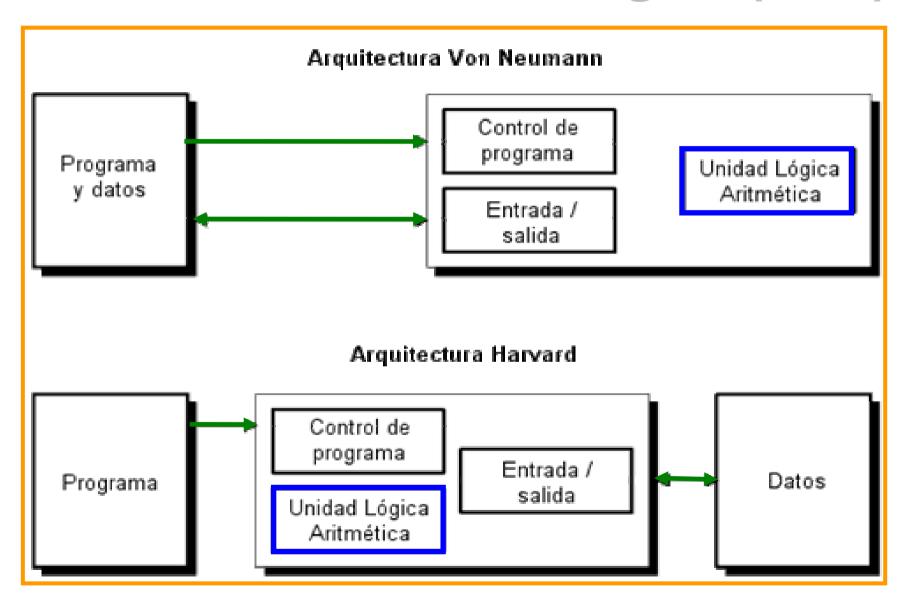

#### Estructura interna básica del DSP

Von-Neuman:

Tipo Harvard:

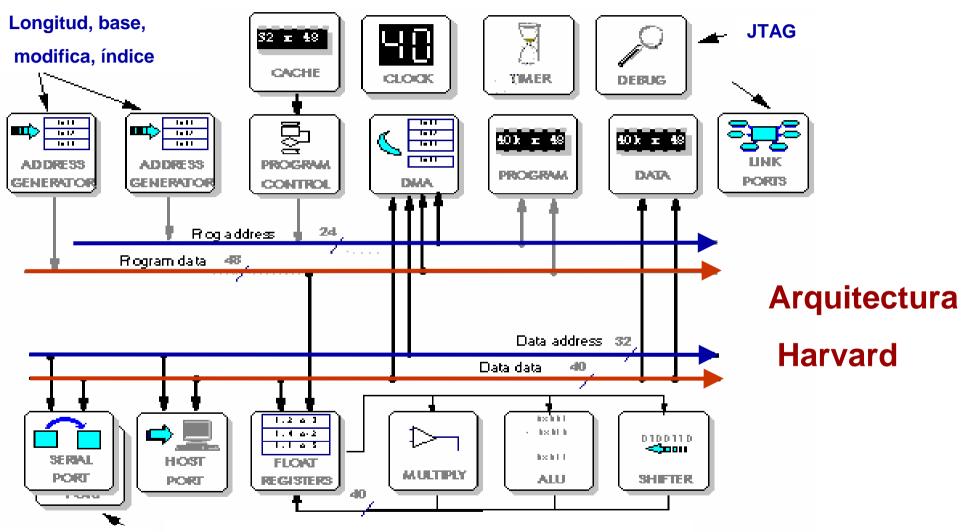

En DSPs predomina la estructura Tipo Harvard

Arquitectura Harvard extendida o super arquitectura Harvard: con memoria caché para almacenar instrucciones que serán reutilizadas.

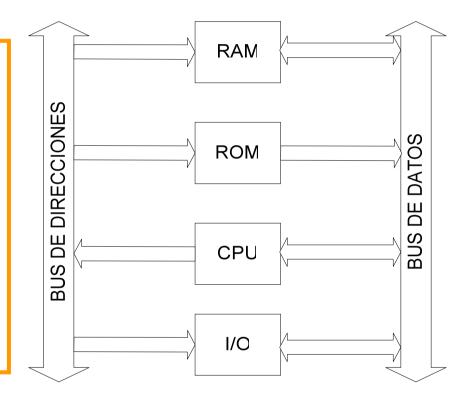

# Arquitectura tipo Von-Neuman

1<sup>er</sup> Paso: Sistema microprocesador accede a la memoria del programa para recoger instrucción a ejecutar.

2<sup>do</sup> Paso: Decodifica instrucción.

3<sup>er</sup> Paso: Accede a la memoria de datos para leer operandos asociados a la instrucción leída.

4º Paso: Se ejecuta la instrucción.

5º Paso: Comienza nuevo ciclo.

- Instrucciones y datos almacenados en memorias (RAM o ROM), a las que accede la Unidad Central de Procesos (CPU) a través de un único bus de direcciones y datos.

- Programas y datos en la misma memoria. No permite accesos a memoria múltiples.

- El microprocesador puede leer y escribir datos en dispositivos externos mediante buffers E/S.

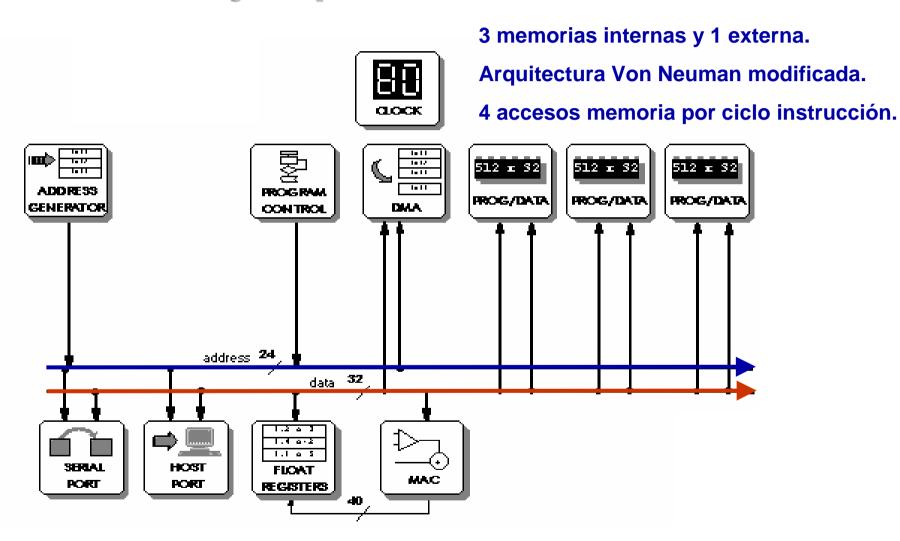

### Arquitectura tipo Von-Neuman modificada

Permite acceso a memoria múltiple por ciclo de instrucción con reloj de memoria más rápido que el ciclo de instrucción.

#### Ejemplo: DSP32C

- Reloj a 80MHz: dividido por cuatro para dar 20 millones de instrucciones por segundo (MIPS).

- Reloj memoria a 80 MHz.

- Cada ciclo de instrucción dividida en 4 máquinas de estado.

- Acceso a memoria en cada máquina de estado

- Permite 4 accesos a memoria por ciclo de instrucción (lectura instrucción, operandos necesitados, almacenamiento resultado)

4 máquinas de estado

|  | STATE    | 3 | 0 | 1 | 2 | 3 | 0 | 1 | 2 | 3 | 0 | 1 | 2 | 3 | 0 | 1 | 2 | 3 | 0 | 1 |

|--|----------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | DATA BUS | I |   |   |   |   |   | X | Y |   |   |   |   |   |   |   |   |   | Z |   |

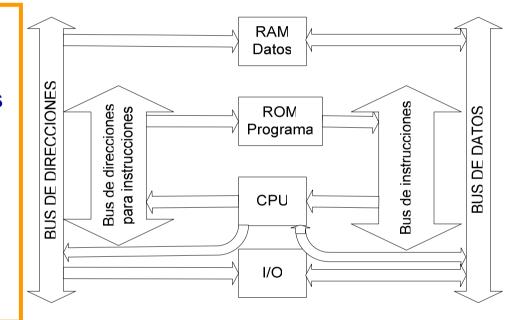

# **Arquitectura tipo Harvard**

1<sup>er</sup> Paso: CPU lee las instrucciones de la memoria mediante el bus de datos.

**2**<sup>do</sup> **Paso**: Ejecuta las instrucciones leídas previamente.

3<sup>er</sup> Paso: Accede a la memoria de datos para leer operandos asociados a la instrucción leída.

4º Paso: Acceso a datos y ejecución de instrucciones en paralelo (pipeling).

- Se simultanea acceso a las memorias de programa y datos

- Presenta menor tiempo de ejecución que la Von-Neuman.

- El hardware destinado a procesar datos y ejecutar instrucciones reside en distintas partes de la CPU.

#### Periféricos

- Puertos de entrada / salida.

- Patillas de interrupción externa.

- Unidades de comunicación serie (RS 232).

- Temporizadores.

- Contadores.

- Bucles enganchados en fase (PLL).

- Buses I2C y/o SPI.

- Convertidores A/D y D/A.

- Módulos de control de ancho de pulso.

# La unidad aritmético lógica (ALU)

# Diagrama de DSP generalizado

## Ejemplo: DSP32C

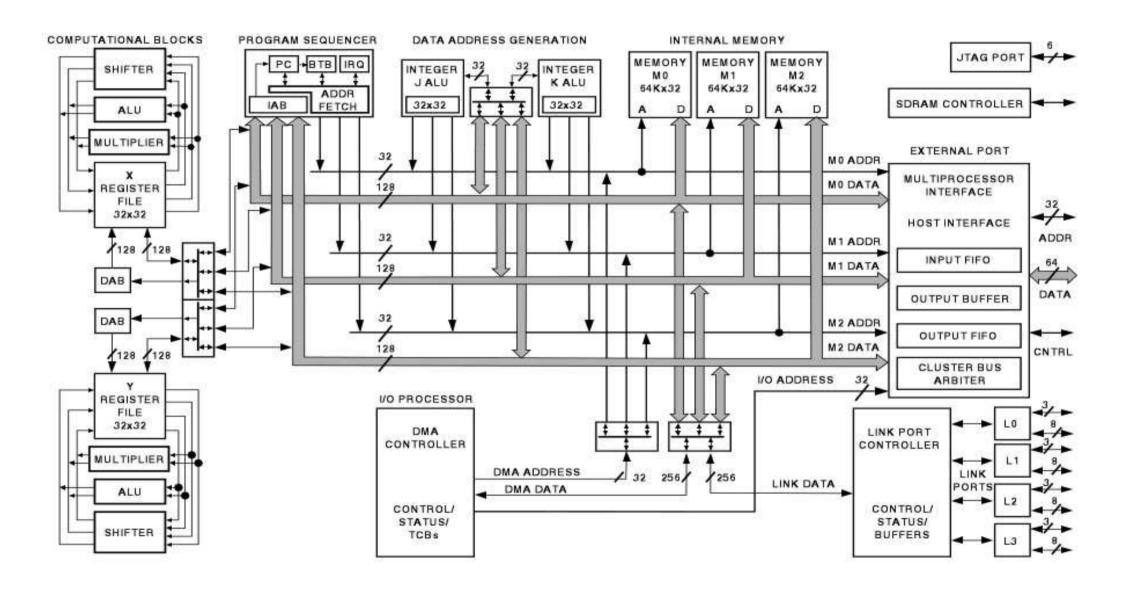

### **Ejemplo: Analog Devices ADSP21060**

Dos puertos serie

### Aplicaciones de DSPs en aviónica (I)

- Aplicaciones digitales genéricas:

- Ventanas de adquisición.

- Convolución.

- Correlación.

- Transformada de Hiltbert.

- Transformada rápida de Fourier.

- Filtrado digital.

- Generación formas de onda,...

- Aplicaciones específicas aviónica:

- Control de motores.

- Control convertidores.

- Computadores control vuelo.

- Displays.

- Sistemas de navegación.

- Guiado de misiles.

- Sistemas de grabación de datos de vuelo.

- Sistemas integrados,...

### Aplicaciones de DSPs en aviónica (II)

#### Telecomunicaciones:

- Teléfonos GSM.

- Cancelación ecos.

- Multiplexado de canales.

- Ecualizadores adptativos.

- Transmisión de voz.

- Etc.

### Aplicaciones de DSPs en aviónica (III)

#### Militar:

- Navegación.

- Sónar.

- Procesado de imágenes.

- Radar.

- Guía de misiles.

- Seguridad en las comunicaciones.

#### Control:

- Robótica.

- Control motores.

- Servocontrol

#### Otros:

- Cancelación ruidos.

- Navegación.

- Análisis de vibraciones.

#### **DSP vs FPGA**

En sector militar se usan diseños heterogéneos donde se emplean DSPs junto a FPGAs.

Las FPGAs se usa para pre-procesamiento, coprocesamiento, control E/S, rutado, etc.

Las FPGAs requieren programación específica.

#### Principales fabricantes de DSPs

- Analog Devices

- Hitachi

- Motorola

- NEC

- SGS-Thomson

- Texas Instruments

- Zilog.

#### **Texas Instruments: DSP**

Principal constructor de DSP en ámbito militar.

Dispone de un encapsulado de plástico (EP) especializado para aplicaciones militares.

La clase V de sus productos está destinada a aplicaciones espaciales

#### **TI: Productos**

✓ TMS320C6000 High Performance DSPs:

TMS320C62x DSPs TMS320C64x DSPs TMS320C67x DSPs

- ✓ TMS320C5000 Power-Efficient DSPs:

- ✓ TMS320C54x DSPs

- ✓ TMS320C55x DSPs

- ✓ TMS320C2000 Digital Signal Controllers:

TMS320C24x Controllers TMS320C28x Controllers

✓ Otros TMS320 DSPs:

TMS320C33 DSPs

TMS320C1X DSPs

TMS320C2X DSPs

TMS320C3X DSPs

TMS320C4X DSPs

TMS320C5X DSPs

TMS320C5X DSPs

TMS320C8X DSPs

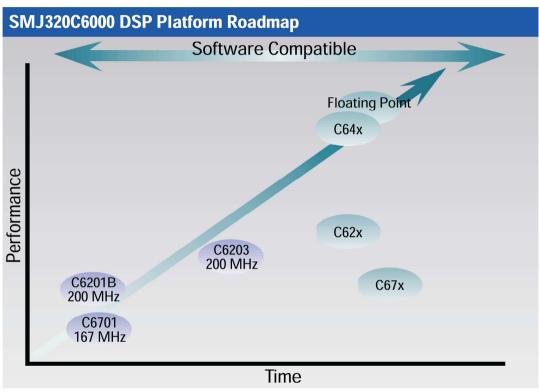

#### TI: Serie C6000

The C6000 DSP platform code-compatible roadmap protects your investment.

- 62x: radar, misiles aire-aire, comunicaciones por satélite...

- 64x: comunicaciones, procesamiento de imágenes...

- 67x: reconocimiento de voz, misiles, radar, radio digital...

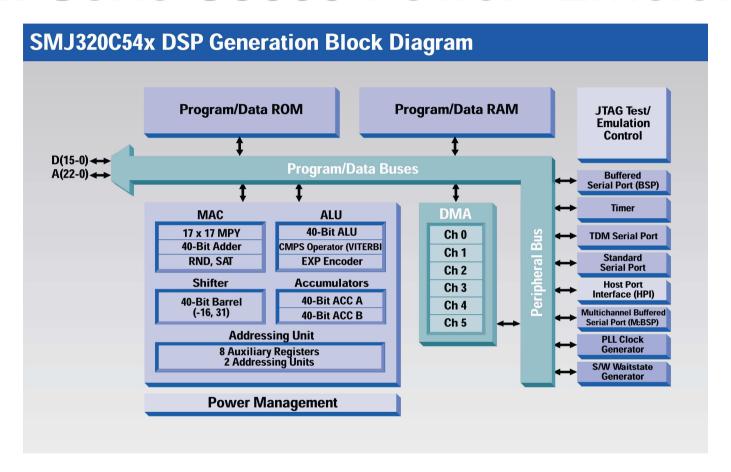

#### TI: Serie C5000 Power- Efficient

54x: se usan sobre todo en comunicaciones

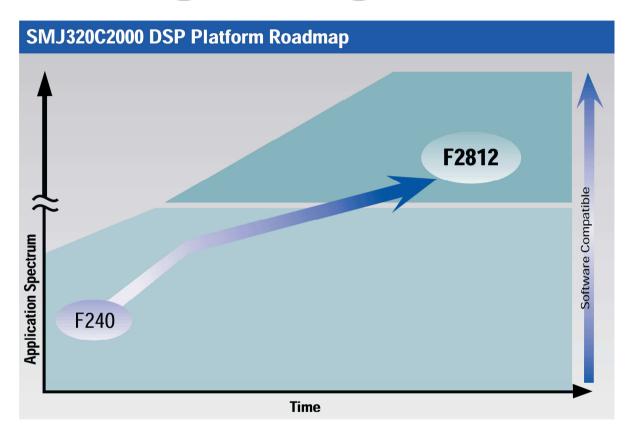

# TI: C2000 Digital Signal Controller

- Serie 24x

- Serie 28x

#### Ambas se emplean en:

- Control de motor.

- Misiles: selección de blancos, guías misiles...

- Comunicaciones: terminal, encriptación...

# **NEC:** la empresa

NEC Electronics Corporation se separó de la empresa NEC y se dedica exclusivamente a semiconductores.

Comercializó el primer DSP.

Tiene su sede en Karawa, Japón

## **NEC:** productos

- Se usan principalmente en comunicación.

- µPD77111

- •µPD77110

- •µPD77111

- •µPD77112

- •µPD77113A

- •µPD77114

- •µPD77115

- μPD77210

- •µPD77210

- •µPD77213

# Zilog: la empresa

- Fundada en 1974 por Federico Faggin

- Sede en San José, California

| Z86295 | Z89321 |

|--------|--------|

| Z89175 | Z89323 |

| Z89223 | Z89371 |

| 789273 | Z89373 |

# **Analog Devices: La empresa**

- Fundada en 1965 por Ray Stata y Matt Lorber.

- Se ha convertido en el segundo productor mundial de DSP.

- Gran multinacional

- -8.900 empleados, 60.000 clientes, 10.000 productos

- Centros en EUA, Irlanda y Filipinas

## **ADI: DSPs**

Aplicaciones en todos los campos: uso médico, industrial, casero, militar...

Sus modelos para todos los rangos: desde nivel usuario a tecnología vanguardia.

Compatibilidad entre modelos: facilita actualización.

## **ADI: DSP, nomenclatura**

### Package (p) Core Voltage (v)\* S = Metric Quad Flat Pack (MQFP) No Designator = 5 V ST = Low-Profile Quad Flat Pack (LQFP) L = 3 MB. B1, B2 = Plastic Ball Grid Array (PBGA) M = 2.5 V Internal (3.3 V I/O) BZ, BZ1, BZ2 = Lead-Free (PBGA) N = 1.8–1.9 V Internal (3.3 V I/O). Z = Ceramio QFP, Heat Slug Up P = 1.6 VW = Ceramic QFP, Heat Slug Down R = 1.2 VP= PLCC 8 = 1.0 VG = PGA\* For Blackfin, TigerSHARC, and BC. CA = Mini-BGA (MBGA) SHARC Processors, this letter refers BCZ. CAZ = Lead-Free (MBGA) to the fabrication process. BP = Thermal-Enhanced FCBGA (SBGA) X-Grade Analog Devices X = Pre-production Digital Signal Processing No Suffix = Production. ADSP-XXxxxvtpp(z or -)qqqX (R or REEL) Tape and Reel Product Number Speed (q) BFxxx = Blackfin Processor ADSP-219x, ADSP-BFxxx. TSxxx = TigerSHARC Processor ADSP-21xxx, ADSP-TSxxx 21xxx = SHARC Processor Speed Grade = Maximum Frequency of Operation 21xx = 16-Bit DSP e.g.: -160 = 160 MHz2199x = Mixed-Signal DSP ADSP-218x, ADSP-2106x Speed Grade = 4 × Maximum Frequency of Operation. e.a.: -160 = 40 MHzTemperature (t) J.K.L.M = Commercial Temp Range\* A.B.C = Industrial Temp Range\* S,T,U = Military Temp Range\* W.Y.Z. = Automotive Temp Range\* "Please refer to individual data sheets for specific range.

## **AD: ADSP-21xx**

Primer modelo de DSP de ADI.

Lenguaje ensamblador fácil de programar y leer.

Diferentes rangos de voltajes, temperaturas, memoria y velocidad.

### **AD: SHARC**

Arquitectura Super Harvard.

- Tres generaciones:

- Primera: 66 MHz, 198 MFlops

- Segunda: 100 MHz, 600 MFlops

- Tercera: 400 MHz, 2.4 GFlops

### **AD: Blackfin**

- Para satisfacer la demanda computacional y las restricciones de potencias de los aplicaciones de audio, video y comunicaciones.

- Une instrucciones de procesamiento y control: simplicidad.

- Velocidad: 750 MHz, 1512 MMACs

- Consumo: menor de 0,15 mW/MMAC a 0,8 V

# **AD: TigerSHARC**

- Mejor de ADI y de los mejores del mercado.

- Para altas exigencias de velocidad y precisión.

- Gran aplicación militar.

| 32-Bit<br>Generic | Speed<br>MHz | Max<br>MMACs | On-Chip<br>Memory | Operating<br>Voltage<br>Core, I/O | Pin/<br>Package   | Price <sup>1</sup><br>(10 K) |

|-------------------|--------------|--------------|-------------------|-----------------------------------|-------------------|------------------------------|

| ADSP-TS101S       | 250          | 2000         | 6M bits           | 1.2 V/3.3 V                       | 625-PBGA/484-PBGA | \$159.00                     |

| ADSP-TS101S       | 300          | 2400         | 6M bits           | 1.2 V/3.3 V                       | 625-PBGA/484-PBGA | \$193.00                     |

| ADSP-TS201S       | 500          | 4000         | 24M bits          | 1.05 V/2.5 V                      | 576-PBGA          | \$186.00                     |

| ADSP-TS201S       | 600          | 4800         | 24M bits          | 1.2 V/2.5 V                       | 576-PBGA          | \$205.00                     |

| ADSP-TS202S       | 500          | 4000         | 12M bits          | 1.05 V/2.5 V                      | 576-PBGA          | \$149.00                     |

| ADSP-TS203S       | 500          | 4000         | 4M bits           | 1.05 V/2.5 V                      | 576-PBGA          | \$47.00                      |

## **Aplicaciones DSP**

- Placas de DSP.

- Aplicaciones espaciales.

### Placas de DSP

Los DSP se montan en placas.

EDO Corp. Desarrolla un sistema inteligencia aeronaval (ALOFTS) que emplea placas de Spectrum Signal Processing.

Incorporan cuatro DSPs Texas Instruments TSM320C6701 a 167 MHz.

# Ejemplo:

## DSP para el espacio

- Aeronáutica y astronáutica íntimamente relacionadas.

- Similitudes (sistemas) y diferencias (requerimientos de radiación).

- En 2001 IBM y Boeing Satellite System crean un DSP para el espacio. Se instaló en un satélite de comunicación.

- Equivale a tres mil ordenadores equipados con Pentiums III

## DSPs aviónica

Operación flexible y en tiempo real. Billones de operaciones por segundo (nuevos aviones 1000 BOPS). Más de 200MB de memoria.

### Avión bombardero estratégico:

- procesamiento paralelo masivo.

- vuelo largo, gran velocidad y baja altura.

- navegación precisa y programación estricta respecto al tiempo.

- ataques a blancos diferentes y múltiples. Diferentes armas y técnicas de lanzamiento.

- readaptación continua y planificación a bordo.

- -datos extremadamente exactos.

Intel i860, dotado de arquitectura RISC: procesamiento en aviones de combate modernos.

Supercomputador ES-1 de Evans & Sutherland: procesamiento paralelo de capacidad moderada. Cuenta con 128 PEs (elementos de procesamiento).

- Highest Performance Floating-Point Digital Signal Processor (DSP)

- '320C40-60:

33-ns Instruction Cycle Time,

330 MOPS, 60 MFLOPS,

30 MIPS, 384M Bytes/s

- '320C40-50:

- 40-ns Instruction Cycle Time

- '320C40-40: 50-ns Instruction Cycle Time

- Six Communications Ports

- Six-Channel Direct Memory Access (DMA) Coprocessor

- Single-Cycle Conversion to and From IEEE-754 Floating-Point Format

- . Single Cycle, 1/x, 1/, x

- Source-Code Compatible With TMS320C3x

- Single-Cycle 40-Bit Floating-Point,

32-Bit Integer Multipliers

- Twelve 40-Bit Registers, Eight Auxiliary Registers, 14 Control Registers, and Two Timers

- IEEE 1149.1<sup>†</sup> (JTAG) Boundary Scan Compatible

- Two Identical External Data and Address Buses Supporting Shared Memory Systems and High Data-Rate, Single-Cycle Transfers:

- High Port-Data Rate of 120M Bytes/s ("C40-60) (Each Burs)

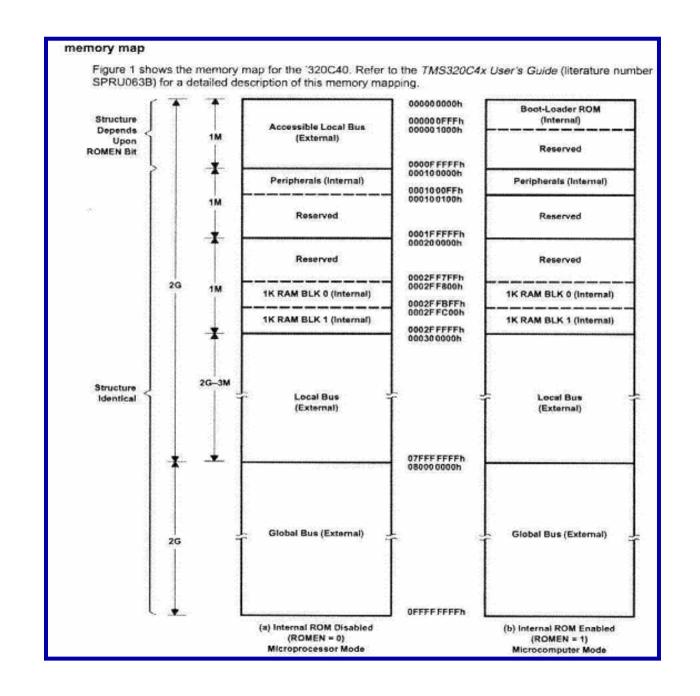

- 16G-Byte Continuous Program/Data/Peripheral Address Space

- Memory-Access Request for Fast, Intelligent Bus Arbitration

- Separate Address-Bus, Data-Bus, and Control-Enable Pins

- Four Sets of Memory-Control Signals Support Different Speed Memories in Hardware

- 325-Pin Ceramic Grid Array (GF Suffix)

- Fabricated Using 0.72-pm Enhanced Performance Implanted CMOS (EPIC \*) Technology by Texas Instruments (TI\*)

- Software-Communication-Port Reset

- NMI With Bus-Grant Peature

#### 335-PIN OF GRID ARRAY PACKAGE IBOTTOM VIEW;2

See Fin Assignmenta beha and Fin Functions sable for location and description of all game.

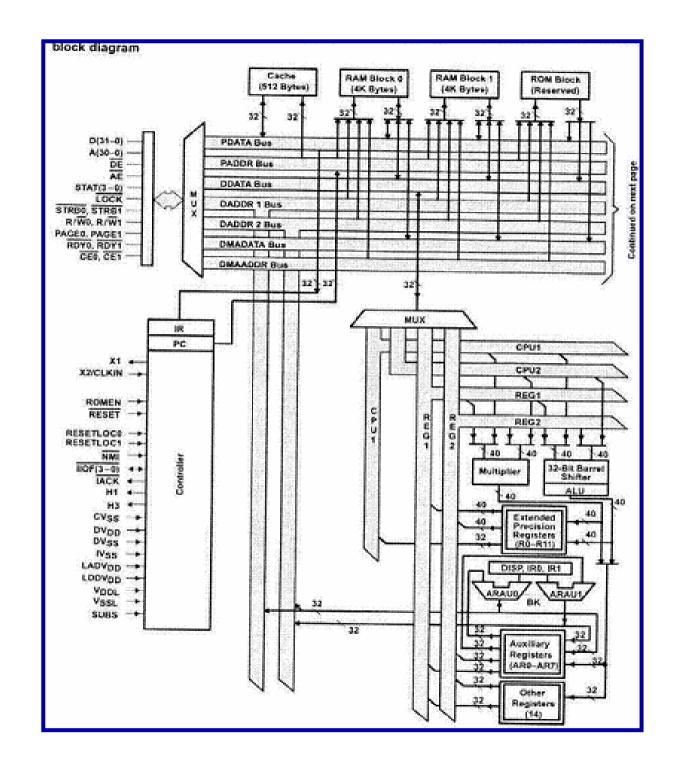

- Separate Internal Program, Data, and DMA Coprocessor Buses for Support of Massive Concurrent Input/Output (I/O) of Program and Data Throughput, Maximizing Sustained Central Processing Unit (CPU) Performance

- On-Chip Program Cache and Dual-Access/Single-Cycle RAM for Increased Memory-Access Performance

- 512-Byte Instruction Cache

- 8K Bytes of Single-Cycle Dual-Access Program or Data RAM

- ROM-Based Boot Loader Supports Program Bootup Using 8-, 16-, or 32-Bit Memories or One of the Communication Ports

- IDLE2 Clock-Stop Power-Down Mode

- 5-V Operation

### TMS320C40

This section lists signal descriptions for the '320C40 device. The '320C40 pin functions table lists each signal, number of pins, operating mode(s) (that is, input, output, or high-impedance state as indicated by I, O, or Z, respectively), and function. The signals are grouped according to function.

Pin Functions

| NAME          | NO. OF<br>PINS | TYPET | DESCRIPTION                                                     | No.    |

|---------------|----------------|-------|-----------------------------------------------------------------|--------|

|               |                |       | GLOBAL-BUS EXTERNAL INTERFACE (80 PINS)                         |        |

| D31-D0        | 32             | 1/0/2 | 32-bit data port of the global-bus external interface           |        |

| DE            | 1              | 3.5   | Data-bus-enable signal for the global-bus external interface.   |        |

| A30-A0        | 31             | 0/2   | 31-bit address port of the global-bus external interface        |        |

| ĀĒ            | 1              | 1     | Address-bus-enable signal for the global-bus external interface | 0.000  |

| STAT3-STAT0   | 4              | 0     | Status signals for the global-bus external interface            |        |

| LOCK          | 3.00           | 0     | Lock signal for the global-bus external interface               |        |

| STRB0‡        | 1              | O/Z   | Access strobe 0 for the global-bus external interface           |        |

| R/Wo‡         | 1              | O/Z   | Read/write signal for STRB0 accesses                            |        |

| PAGE0‡        | 1              | O/Z   | Page signal for STRB0 accesses                                  |        |

| RDY0\$        | 1              | 1     | Ready signal for STRB0 accesses                                 |        |

| CE0‡          | 1              | 1     | Control enable for the STRB0; PAGE0, and R/W0 signals           |        |

| STRB1‡        | 1              | O/Z   | Access strobe 1 for the global-bus external interface           |        |

| R/W1‡         | 1              | O/Z   | Read/write signal for STRB1 accesses                            |        |

| PAGE1‡        | 1              | 0/2   | Page signal for STRB1 accesses                                  |        |

| RDY1‡         | 1              | 1     | Ready signal for STRB1 accesses                                 |        |

| CE1‡          | 1              | 1     | Control enable for the STRB1, PAGE1, and R/W1 signals           |        |

|               |                |       | LOCAL-BUS EXTERNAL INTERFACE (80 PINS)                          |        |

| LD31-LD0      | 32             | 1/O/Z | 32-bit data port of the local-bus external interface            |        |

| LDE           | 1              | 1     | Data-bus-enable signal for the local-bus external interface     |        |

| LA30-LA0      | 31             | O/Z   | 31-bit address port of the local-bus external interface.        |        |

| LAE           | 1              | 1     | Address-bus-enable signal for the local-bus external interface  |        |

| LSTAT3-LSTATO | 4              | 0     | Status signals for the local-bus external interface             |        |

| LLOCK         | 1              | 0     | Lock signal for the local-bus external interface                |        |

| LSTRB0‡       | 1              | O/Z   | Access strobe 0 for the local-bus external interface            | -      |

| LR/W0         | 1              | O/Z   | Read/write signal for LSTRB0 accesses                           |        |

| LPAGE0        | 1              | O/Z   | Page signal for LSTR80 accesses                                 |        |

| LRDYO         | 1              | 1.    | Ready signal for LSTRB0 accesses                                |        |

| LCE0          | 1              |       | Control enable for the LSTRB0, LPAGE0, and LR/W0 signals        |        |

| LSTRB1‡       | 1              | O/Z   | Access strobe 1 for the local-bus external interface            | 10101  |

| LR/W1         | 1              | O/Z   | Read/write signal for LSTRB1 accesses                           |        |

| LPAGE1        | 1              | O/Z   | Page signal for LSTRB1 accesses                                 |        |

| LRDY1         | 1              | 1     | Ready signal for LSTRB1 accesses                                | Grain. |

| LCE1          | 100            |       | Control enable for the LSTRB1, LPAGE1, and LR/W1 signals        | -      |

<sup>†1 =</sup> input. O = output, Z = high impedance

<sup>\$</sup> Signal's effective address range is defined by the local/global STRB ACTIVE bits.

#### description

The '320C40 digital signal processors (DSPs) are 32-bit, floating-point processors manufactured in 0.72-µm, double-level metal CMOS technology. The '320C40 is a part of the fourth generation of DSPs from Texas Instruments and is designed primarily for parallel processing.

#### operation

The '320C40 has six on-chip communication ports for processor-to-processor communication with no external hardware and simple communication software. This allows connectivity to other 'C4x processors with no external-glue logic. The communication ports remove input/output bottlenecks, and the independent smart DMA coprocessor is able to handle the CPU input/output burden.

### central processing unit

The '320C40 CPU is configured for high-speed internal parallelism for the highest sustained performance. The key features of the CPU are:

- Eight operations/cycle:

- 40/32-bit floating-point/integer multiply

- 40/32-bit floating-point/integer ALU operation

- Two data accesses

- Two address register updates

- IEEE floating-point conversion

- Divide and square-root support

- 'C3x assembly language compatibility

- Byte and halfword accessibility

#### DMA coprocessor

The DMA coprocessor allows concurrent I/O and CPU processing for the highest sustained CPU performance. The key features of the DMA processor are:

- Link pointers allow DMA channels to auto-initialize without CPU intervention.

- Parallel CPU operation and DMA transfers

- Six DMA channels support memory-to-memory data transfers.

- Split-mode operation doubles the available DMA channel to 12 when data transfers to and from a communication port are required.

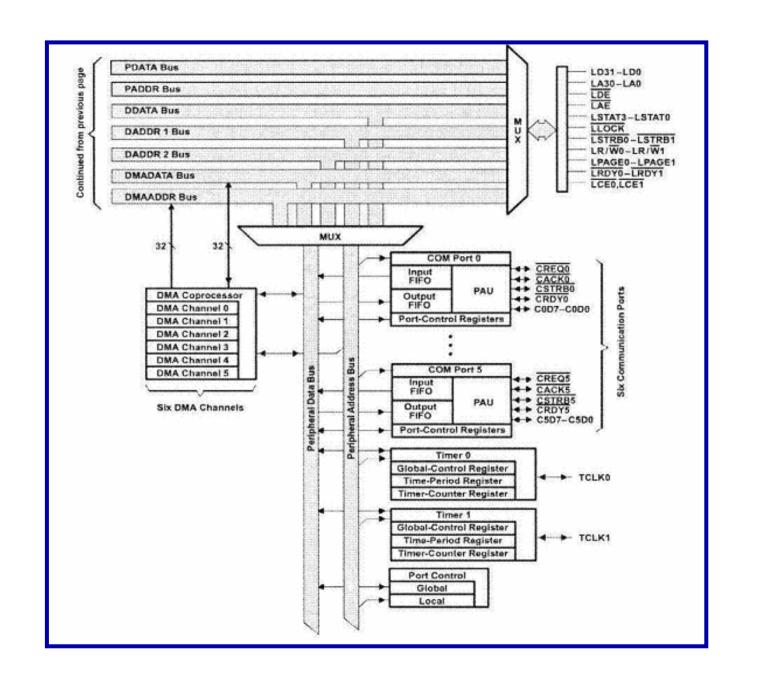

#### communication ports

The '320C40 is the first DSP with on-chip communication ports for processor-to-processor communication with no external hardware and simple communication software. The features of the communication ports are:

- Direct interprocessor communication and processor I/O

- Six communication ports for direct interprocessor communication and processor I/O

- 20M-bytes/s bidirectional interface on each communication port for high-speed multiprocessor interface

- Separate input and output 8-word-deep FIFO buffers for processor-to-processor communication and I/O

- Automatic arbitration and handshaking for direct processor-to-processor connection.